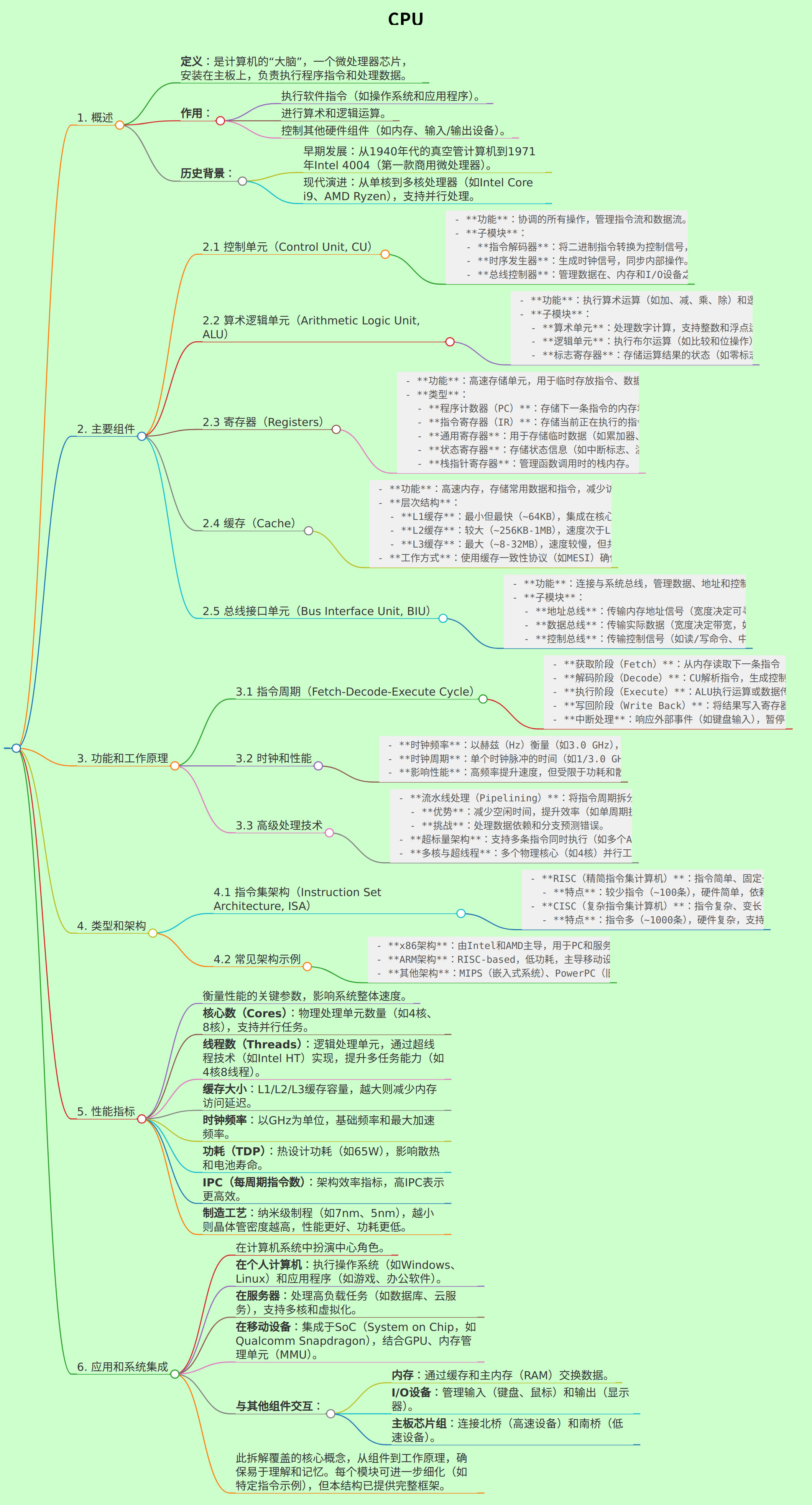

# CPU

- CPU(Central Processing Unit,中央处理器)是计算机的核心部件,负责执行指令、处理数据和控制计算机的整体操作。它基于冯·诺依曼架构设计,包括指令获取、解码、执行和写回等基本过程。以下是CPU的详细拆解,确保准确性和完整性,每个关键内容被拆解为更小的子模块。

## 1. 概述

- **定义**:CPU是计算机的“大脑”,一个微处理器芯片,安装在主板上,负责执行程序指令和处理数据。

- **作用**:

- 执行软件指令(如操作系统和应用程序)。

- 进行算术和逻辑运算。

- 控制其他硬件组件(如内存、输入/输出设备)。

- **历史背景**:

- 早期发展:从1940年代的真空管计算机到1971年Intel 4004(第一款商用微处理器)。

- 现代演进:从单核到多核处理器(如Intel Core i9、AMD Ryzen),支持并行处理。

## 2. 主要组件

- CPU内部由多个功能单元组成,这些单元协同工作以执行指令。

### 2.1 控制单元(Control Unit, CU)

- **功能**:协调CPU的所有操作,管理指令流和数据流。

- **子模块**:

- **指令解码器**:将二进制指令转换为控制信号,指导其他单元执行。

- **时序发生器**:生成时钟信号,同步CPU内部操作。

- **总线控制器**:管理数据在CPU、内存和I/O设备之间的传输。

### 2.2 算术逻辑单元(Arithmetic Logic Unit, ALU)

- **功能**:执行算术运算(如加、减、乘、除)和逻辑运算(如AND、OR、NOT)。

- **子模块**:

- **算术单元**:处理数字计算,支持整数和浮点运算。

- **逻辑单元**:执行布尔运算(如比较和位操作)。

- **标志寄存器**:存储运算结果的状态(如零标志、进位标志),用于条件分支。

### 2.3 寄存器(Registers)

- **功能**:高速存储单元,用于临时存放指令、数据和地址,提升访问速度。

- **类型**:

- **程序计数器(PC)**:存储下一条指令的内存地址。

- **指令寄存器(IR)**:存储当前正在执行的指令。

- **通用寄存器**:用于存储临时数据(如累加器、基址寄存器),数量由架构决定(如x86有16个)。

- **状态寄存器**:存储CPU状态信息(如中断标志、溢出标志)。

- **栈指针寄存器**:管理函数调用时的栈内存。

### 2.4 缓存(Cache)

- **功能**:高速内存,存储常用数据和指令,减少访问主内存的延迟。

- **层次结构**:

- **L1缓存**:最小但最快(~64KB),集成在CPU核心内,分指令缓存(L1I)和数据缓存(L1D)。

- **L2缓存**:较大(~256KB-1MB),速度次于L1,通常共享于核心。

- **L3缓存**:最大(~8-32MB),速度较慢,但共享于多个核心,提高多任务性能。

- **工作方式**:使用缓存一致性协议(如MESI)确保多核间数据同步。

### 2.5 总线接口单元(Bus Interface Unit, BIU)

- **功能**:连接CPU与系统总线,管理数据、地址和控制信号的传输。

- **子模块**:

- **地址总线**:传输内存地址信号(宽度决定可寻址空间,如64位支持16EB)。

- **数据总线**:传输实际数据(宽度决定带宽,如64位总线)。

- **控制总线**:传输控制信号(如读/写命令、中断请求)。

## 3. 功能和工作原理

- CPU通过指令周期执行任务,每个周期包括多个阶段。

### 3.1 指令周期(Fetch-Decode-Execute Cycle)

- **获取阶段(Fetch)**:从内存读取下一条指令(地址由PC提供),存入IR。

- **解码阶段(Decode)**:CU解析指令,生成控制信号。

- **执行阶段(Execute)**:ALU执行运算或数据传输。

- **写回阶段(Write Back)**:将结果写入寄存器或内存,更新PC指向下一条指令。

- **中断处理**:响应外部事件(如键盘输入),暂停当前任务,执行中断服务程序。

### 3.2 时钟和性能

- **时钟频率**:以赫兹(Hz)衡量(如3.0 GHz),表示每秒周期数;频率越高,执行速度越快。

- **时钟周期**:单个时钟脉冲的时间(如1/3.0 GHz ≈ 0.33纳秒),每个指令周期占用多个时钟周期。

- **影响性能**:高频率提升速度,但受限于功耗和散热;现代CPU使用动态频率调整(如Intel Turbo Boost)。

### 3.3 高级处理技术

- **流水线处理(Pipelining)**:将指令周期拆分为并行阶段(如5级流水线),允许多条指令同时处理,提高吞吐量。

- **优势**:减少空闲时间,提升效率(如单周期执行变为多指令重叠)。

- **挑战**:处理数据依赖和分支预测错误。

- **超标量架构**:支持多条指令同时执行(如多个ALU)。

- **多核与超线程**:多个物理核心(如4核)并行工作;超线程(Hyper-Threading)使单核模拟多逻辑核心,提升多任务性能。

## 4. 类型和架构

- CPU设计基于指令集架构(ISA),决定指令格式和执行方式。

### 4.1 指令集架构(Instruction Set Architecture, ISA)

- **RISC(精简指令集计算机)**:指令简单、固定长度(如ARM、RISC-V),执行快、功耗低,适合移动设备。

- **特点**:较少指令(~100条),硬件简单,依赖编译器优化。

- **CISC(复杂指令集计算机)**:指令复杂、变长(如x86),单条指令完成多操作,适合桌面/服务器。

- **特点**:指令多(~1000条),硬件复杂,支持高级功能(如内存管理)。

### 4.2 常见架构示例

- **x86架构**:由Intel和AMD主导,用于PC和服务器(如Intel Core系列),支持CISC。

- **ARM架构**:RISC-based,低功耗,主导移动设备(如智能手机的Apple A系列芯片)。

- **其他架构**:MIPS(嵌入式系统)、PowerPC(旧款Mac)。

## 5. 性能指标

- 衡量CPU性能的关键参数,影响系统整体速度。

- **核心数(Cores)**:物理处理单元数量(如4核、8核),支持并行任务。

- **线程数(Threads)**:逻辑处理单元,通过超线程技术(如Intel HT)实现,提升多任务能力(如4核8线程)。

- **缓存大小**:L1/L2/L3缓存容量,越大则减少内存访问延迟。

- **时钟频率**:以GHz为单位,基础频率和最大加速频率。

- **功耗(TDP)**:热设计功耗(如65W),影响散热和电池寿命。

- **IPC(每周期指令数)**:架构效率指标,高IPC表示更高效。

- **制造工艺**:纳米级制程(如7nm、5nm),越小则晶体管密度越高,性能更好、功耗更低。

## 6. 应用和系统集成

- CPU在计算机系统中扮演中心角色。

- **在个人计算机**:执行操作系统(如Windows、Linux)和应用程序(如游戏、办公软件)。

- **在服务器**:处理高负载任务(如数据库、云服务),支持多核和虚拟化。

- **在移动设备**:集成于SoC(System on Chip,如Qualcomm Snapdragon),结合GPU、内存管理单元(MMU)。

- **与其他组件交互**:

- **内存**:通过缓存和主内存(RAM)交换数据。

- **I/O设备**:管理输入(键盘、鼠标)和输出(显示器)。

- **主板芯片组**:连接北桥(高速设备)和南桥(低速设备)。

- 此拆解覆盖CPU的核心概念,从组件到工作原理,确保易于理解和记忆。每个模块可进一步细化(如特定指令示例),但本结构已提供完整框架。

复制内容

下载markdown文件

在线编辑